**Evaluation Board Document**

**μPC8233TK-EV09-A**

**Evaluation Board**

- Circuit Description

- Typical performance data

- Power gain and isolation plots

- Input and output return loss plots

- o Circuit schematic and assembly drawing

Circuit Description

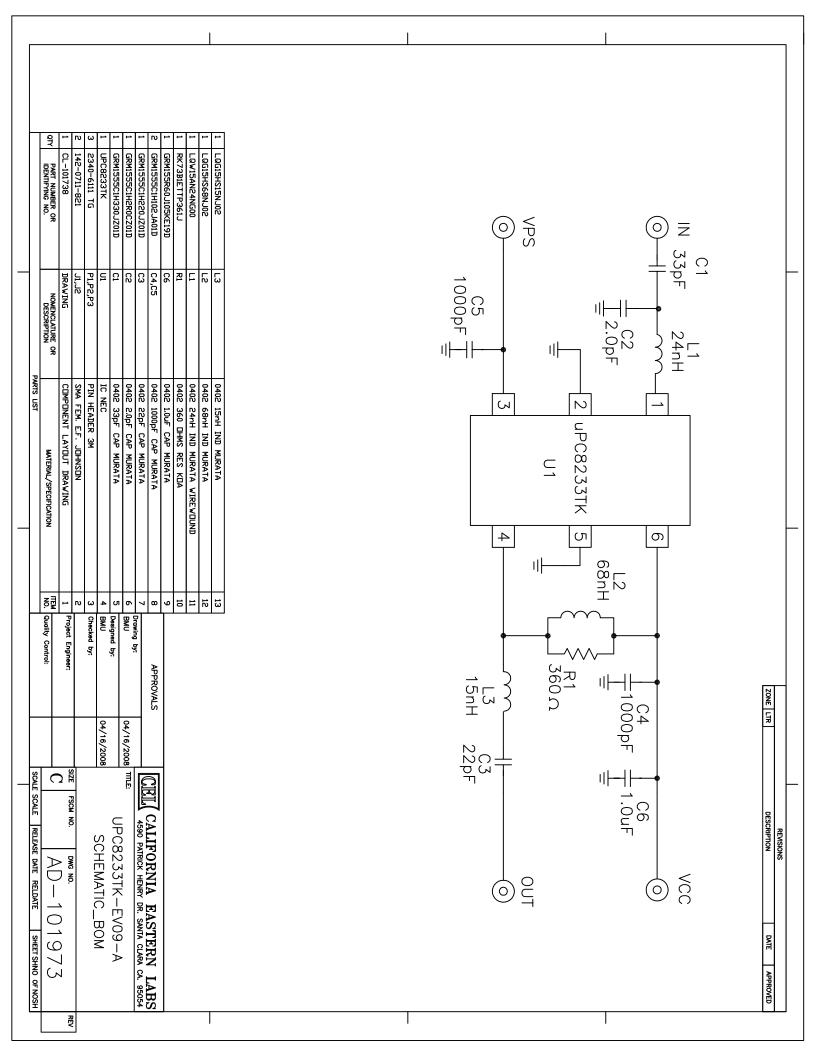

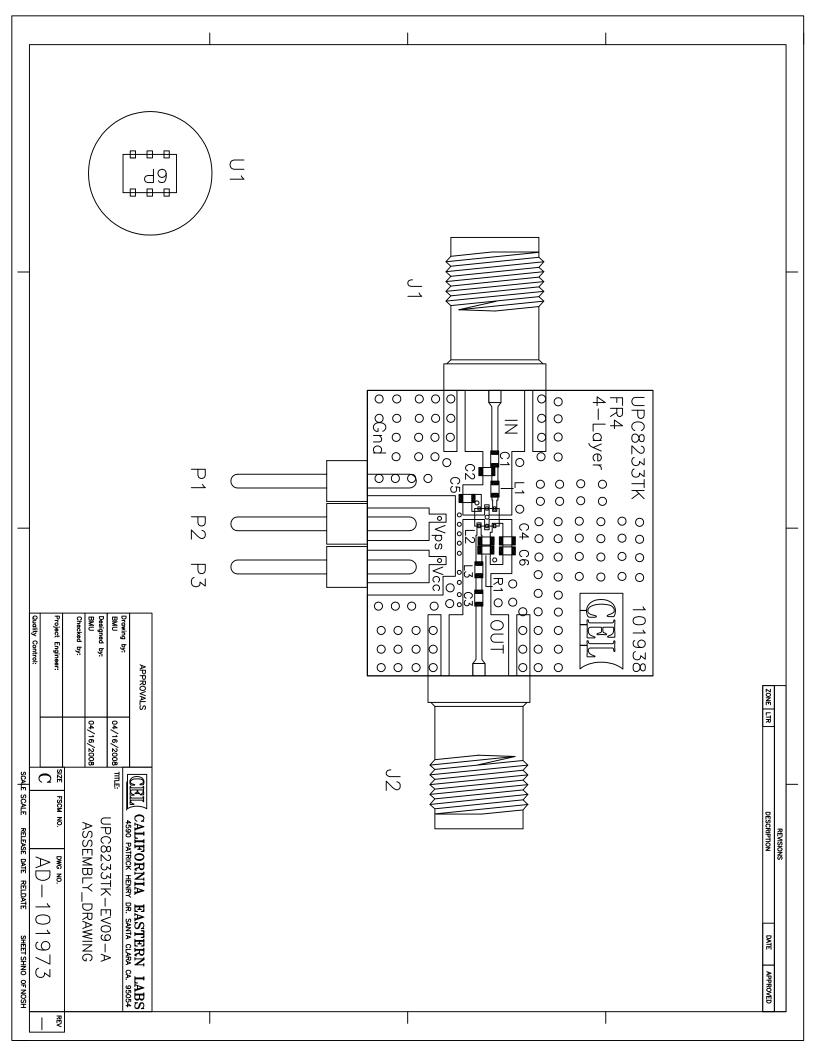

The circuit schematic and assembly drawing are shown on the last two pages.

**Matching Circuits**

The output matching is mainly through L3 and it should be placed close to the device.

The input matching consists of L1 and C2, and C1 is used for DC block For applications where noise figure is critically important, a high Q inductor, such as wire-wound type, is recommended over regular chip inductor for L1. Using high Q inductors can improve the noise figure by about 0.05dB. The values of L1 and C2 used on this evaluation circuit are chosen for a reasonable balance between input return loss and noise figure. A further trade-off can be made between these two parameters by adjusting the values of L1 and/or C2.

**PCB Material**

The PCB is FR4 four layer board. The top and bottom dielectric layers are 8mil thick. The total board thickness is 62mil.

## **Typical Performance Data**

Test Conditions:

f=915MHz; Vcc=Vps=1.8V

**Noise Figure**: 1.3dB (direct measurement on board, no subtraction of board loss)

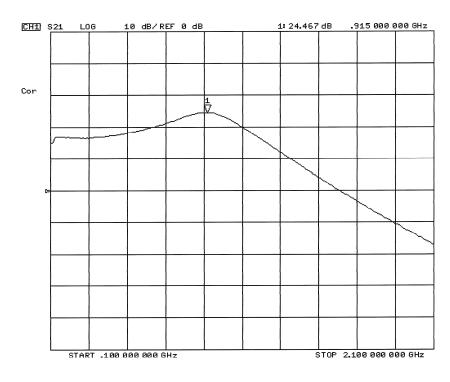

Gain: 24dB

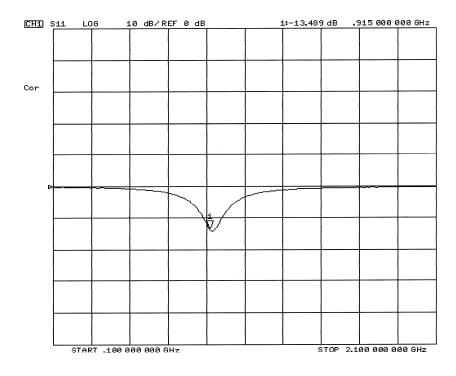

**Input return loss:** -12dB

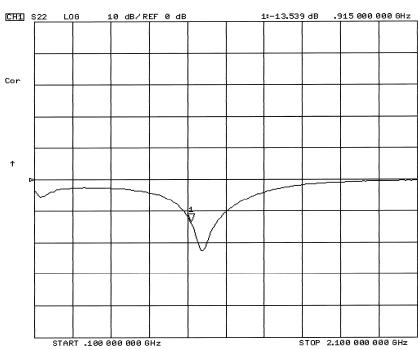

Output return loss: -13dB

IP1dB: -29dBm

**IIP3**: -20dBm

2

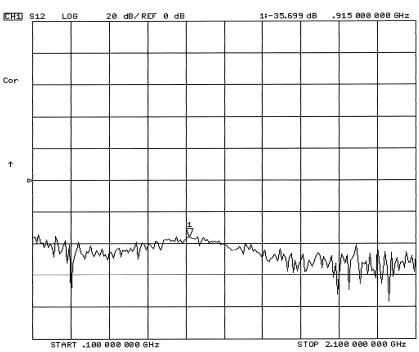

## Power Gain and Isolation Plots

## Input and Output Return Loss Plots